- 您现在的位置:买卖IC网 > Sheet目录3881 > PIC18F8585T-I/PT (Microchip Technology)IC PIC MCU FLASH 24KX16 80TQFP

PIC18F6585/8585/6680/8680

DS30491C-page 350

2004 Microchip Technology Inc.

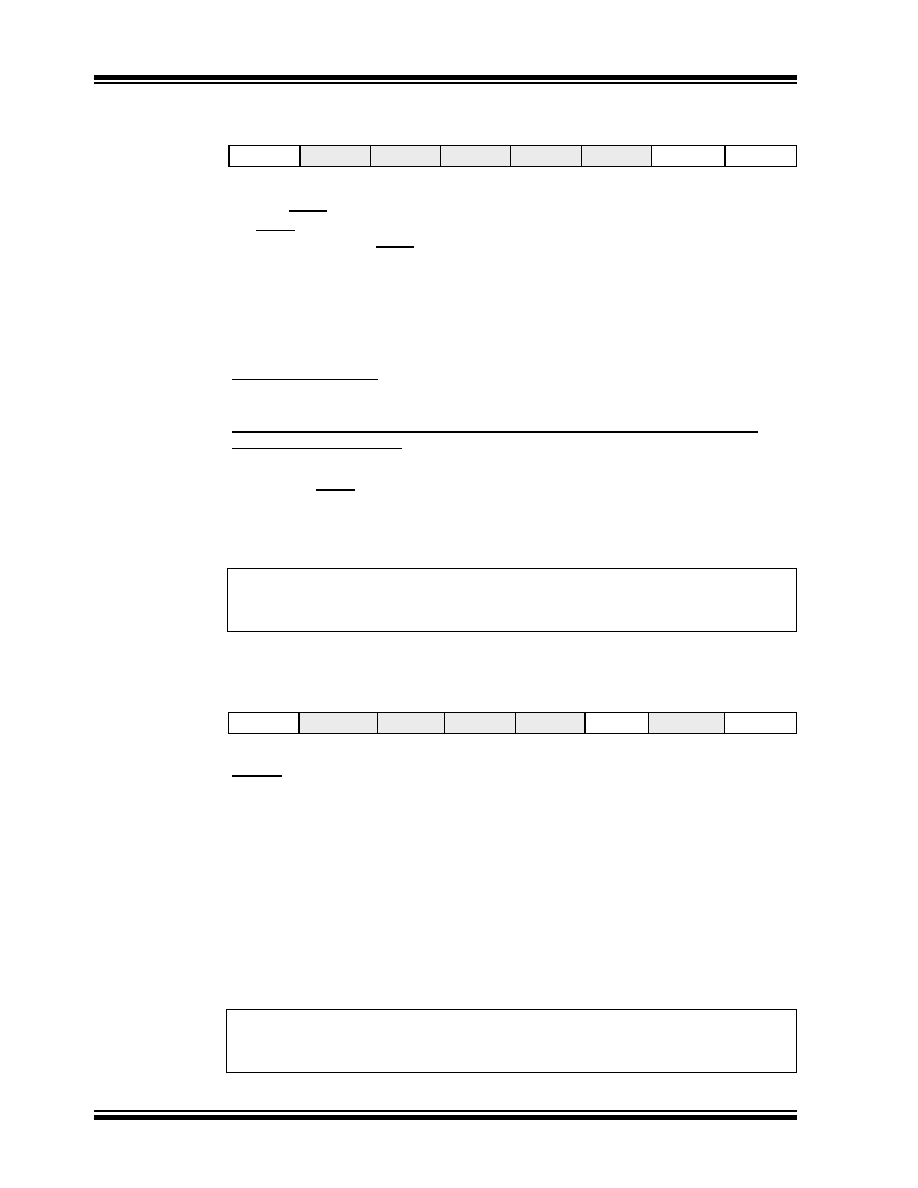

REGISTER 24-5:

CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

REGISTER 24-6:

CONFIG4L: CONFIGURATION REGISTER 4 LOW (BYTE ADDRESS 300006h)

R/P-1

U-0

R/P-1

MCLRE

—

ECCPMX

CCP2MX

bit 7

bit 0

bit 7

MCLRE: MCLR Enable bit(1)

1

= MCLR pin enabled, RG5 input pin disabled

0

= RG5 input enabled, MCLR disabled

bit 6-2

Unimplemented: Read as ‘0’

bit 1

ECCPMX: CCP1 PWM outputs P1B, P1C mux bit (PIC18F8X8X devices only)(2)

1

= P1B, P1C are multiplexed with RE6, RE5

0

= P1B, P1C are multiplexed with RH7, RH6

bit 0

CCP2MX: CCP2 Mux bit

In Microcontroller mode:

1

= CCP2 input/output is multiplexed with RC1

0

= CCP2 input/output is multiplexed with RE7

In Microprocessor, Microprocessor with Boot Block and Extended Microcontroller modes

(PIC18F8X8X devices only):

1

= CCP2 input/output is multiplexed with RC1

0

= CCP2 input/output is multiplexed with RB3

Note 1: If MCLR is disabled, either disable low-voltage ICSP or hold RB5/PGM low to

ensure proper entry into ICSP mode.

2: Reserved for PIC18F6X8X devices; maintain this bit set.

Legend:

R = Readable bit

P = Programmable bit

U = Unimplemented bit, read as ‘0’

- n = Value when device is unprogrammed

u = Unchanged from programmed state

R/P-1

U-0

R/P-1

U-0

R/P-1

DEBUG

—

—LVP

—STVREN

bit 7

bit 0

bit 7

DEBUG: Background Debugger Enable bit

1

= Background debugger disabled. RB6 and RB7 configured as general purpose I/O pins.

0

= Background debugger enabled. RB6 and RB7 are dedicated to in-circuit debug.

bit 6-3

Unimplemented: Read as ‘0’

bit 2

LVP: Low-Voltage ICSP Enable bit

1

= Low-voltage ICSP enabled

0

= Low-voltage ICSP disabled

bit 1

Unimplemented: Read as ‘0’

bit 0

STVREN: Stack Full/Underflow Reset Enable bit

1

= Stack full/underflow will cause Reset

0

= Stack full/underflow will not cause Reset

Legend:

R = Readable bit

P = Programmable bit

U = Unimplemented bit, read as ‘0’

- n = Value when device is unprogrammed

u = Unchanged from programmed state

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

XF2J-2424-11

CONN FPC 24POS 0.5MM SMT

PIC18LF6585T-I/PT

IC PIC MCU FLASH 24KX16 64TQFP

PIC18LF6680T-I/PT

IC PIC MCU FLASH 32KX16 64TQFP

XF2J-2224-11

CONN FPC 22POS 0.5MM SMT

PIC18F6525T-I/PT

IC PIC MCU FLASH 24KX16 64TQFP

PIC18F4439-E/ML

IC PIC MCU FLASH 6KX16 44QFN

XF2J-2024-11

CONN FPC 20POS 0.5MM SMT

PIC16LF747-I/ML

IC PIC MCU FLASH 4KX14 44QFN

相关代理商/技术参数

PIC18F85J10-I/PT

功能描述:8位微控制器 -MCU 32 KB FL 2 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J10-I/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT MCU PIC18F 40MHZ TQFP-80 制造商:Microchip Technology Inc 功能描述:IC, 8BIT MCU, PIC18F, 40MHZ, TQFP-80

PIC18F85J10T-I/PT

功能描述:8位微控制器 -MCU 32 KB FL 2 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J11-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 2048BRAM 67I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J11T-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 2048bytes-RAM 67I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J15-I/PT

功能描述:8位微控制器 -MCU 48 KB FL 4 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J15T-I/PT

功能描述:8位微控制器 -MCU 48 KB FL 4 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J50-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 3936byte RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT